An AlGaAs/InGaAs Pseudomorphic High Electron Mobility Transistor (PHEMT)

For X- and Ku-band Power Applications

John C. Huang, G. Jackson, S. Shanfield, W. Hoke, P. Lyman, D. Atwood,

P. Saledas, M. Schindler, Y. Tajima, A. Platzker, D. Massé and H. Statz

Raytheon Co., Research Division, 131 Spring St., Lexington, MA 02173

Abstract

A PHEMT with simultaneous record-high output power, gain and power-added efficiency at 10 and 18 GHz has been achieved due to the use of a new method to improve the gate-drain reverse breakdown voltage. A critical surface problem was uncovered and resolved. Silicon nitride was deposited as surface passivation.

It is well known that the GaAs Pseudomorphic High Electron Mobility Transistor (PHEMT) is currently the best room temperature low noise transistor on GaAs substrates. Past attempts to modify this device for power applications have been met with limited success because of low gate-drain reverse breakdown voltage (BV<sub>gd</sub>). Here we report a technique to improve BV<sub>gd</sub> without introducing undesirable side effects such as "parasitic gating" by surface states (to be described). Improving the BV<sub>gd</sub> has led to the demonstration of a state-of-the-art power PHEMT for X- and Ku-band operations, for which the MESFET is considered the best candidate.

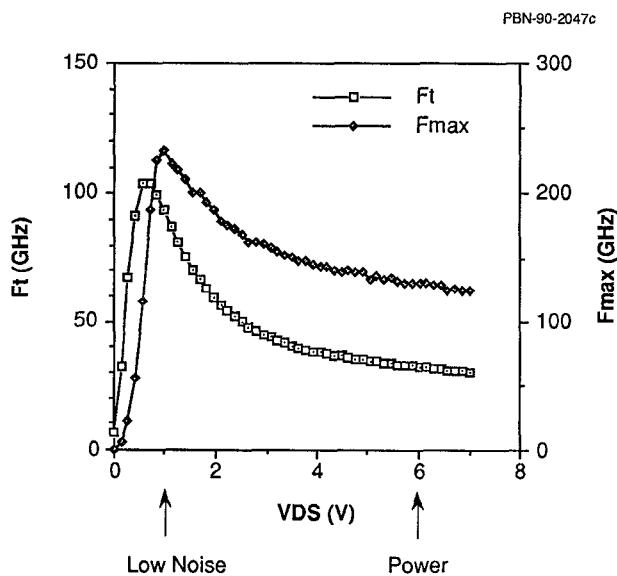

The modified PHEMT exhibited a BV<sub>gd</sub> of 12 to 16 V, thereby allowing a drain bias of 8.5 V. The power performance of this device is summarized in Table 1, where a comparison has also been made with the best published power transistor results, emphasizing in particular the figure-of-merit for efficiency. This power device also exhibited minimum noise figures of 0.9 dB with 11.3 dB gain at 10 GHz and 1.5 dB with 8 dB gain at 18 GHz. A current-gain cut-off frequency (F<sub>t</sub>) of 100 GHz and a maximum-available-gain cut-off frequency (F<sub>max</sub>) of 230 GHz at low drain voltages (<2 V) were extrapolated from S-parameters measured up to 26 GHz. A rf voltage gain of 80 was also realized. To the best of our knowledge, this device has exhibited the best X- and Ku-band CW power performance of all transistors in terms of achieving high power added efficiency, output power and power gain simultaneously.

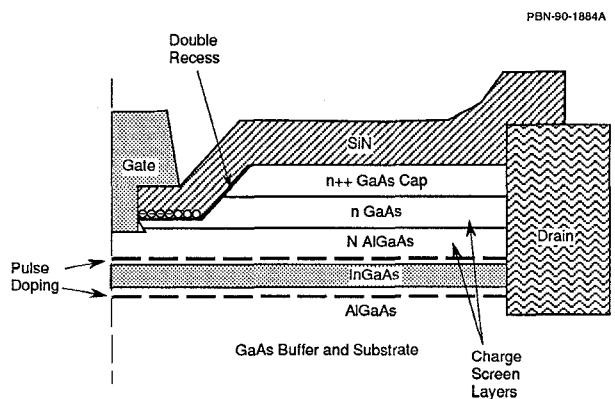

The PHEMT epitaxial structure consists of a single quantum well with two pulse doping planes on either side of the In<sub>0.16</sub>Ga<sub>0.85</sub>As conduction channel. The epitaxial layers, as shown in Figure 1, were grown by MBE. This device was fabricated using a conventional Schottky-barrier FET process with a double-recessed gate trench. Electron beam lithography was used to write 0.33- to 0.4- $\mu$ m gates with both "T" and conventional cross-sections; SiN was deposited as surface passivation. Comparable performance has been obtained from three separate lots processed thus far.

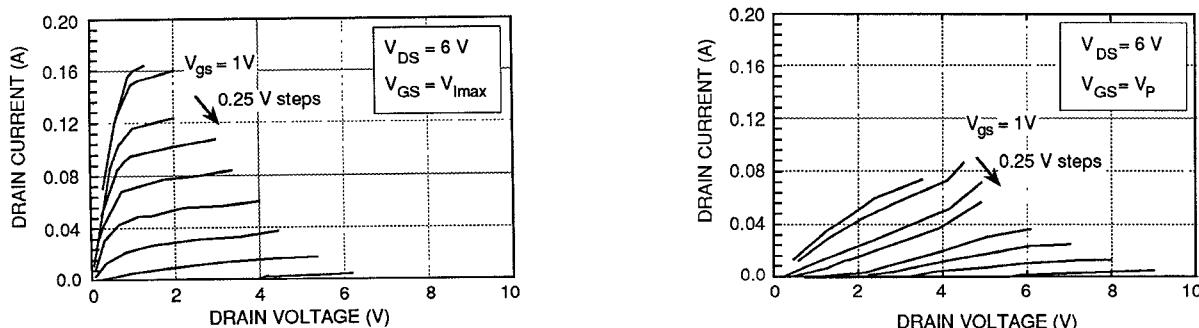

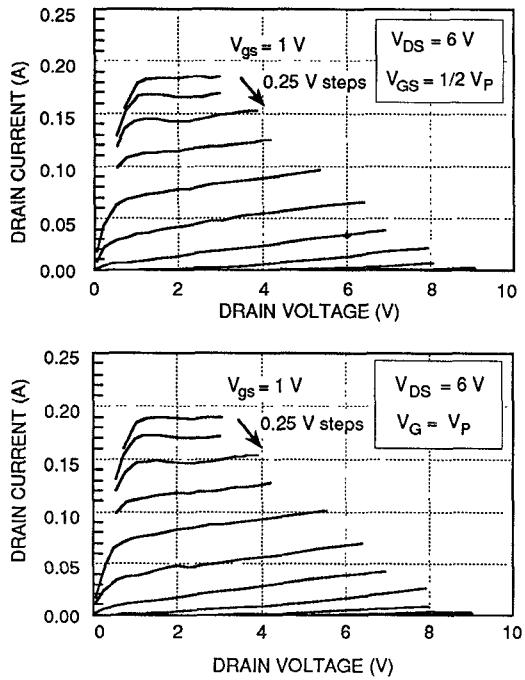

In the course of improving the BV<sub>gd</sub>, a heretofore unreported problem of "parasitic gating" by surface states in wide-recessed, pulse-doped PHEMTs was encountered. This problem manifests itself in pulsed current-voltage (I-V) characteristics that are dependent on the DC bias origin, with progressively worse characteristics as either drain bias voltage increases or gate bias voltage becomes more negative. The pulsed I-V curves for several DC bias points shown in Figures 2a and 2b best illustrate this phenomenon. Similar symptoms have been observed in MESFETs by Platzker et al<sup>[1]</sup>. This effect may have thwarted earlier efforts to improve the power performance of PHEMTs.

U

This "parasitic gating" is due to naturally occurring mid-gap energy states residing on the surface of the adjacent recessed regions of the gate, particularly on the drain side<sup>[2]</sup>. These states trap electrons, and their density and spatial distribution<sup>[3]</sup> are determined by the gate-drain potential. At equilibrium these ionized surface states are compensated by a space charge zone underneath the surface, and their response to changing gate-drain potentials requires milliseconds of charging (discharging) time. The result is a quiescent depletion zone which modulates the conduction channel in the drain region with the DC gate-drain potential dictating the extent of the modulation. In such manner the slow-responding depletion zone undermines the pulsed I-V behavior of a transistor.

We engineered around this surface state problem by incorporating a double-recessed gate process and a charge screen comprised of lightly doped GaAs and AlGaAs layers (refer to Figure 1); combined, these two features maintained the high BV<sub>gd</sub> of wide-recessed, pulse-doped PHEMTs without causing a degradation in the transistor's RF drain current. We surmise that the double-recess profile reduces the surface electric field and the doped layers shield the channel from the residual surface charges, in addition to reducing the channel access resistance. The n-GaAs is needed to prevent oxidation of the AlGaAs layer. The bias-dependence of the pulsed I-V characteristics has been largely eliminated as shown in Figures 2c and 2d.

The BV<sub>gd</sub> was increased from 3-8 V for the conventional PHEMT to 12-16 V for the power PHEMT described here. We note that breakdown voltages (at 1mA/mm leakage current) ranging up to 20 V could be achieved. However, our work showed that there is a tradeoff between BV<sub>gd</sub> and the amount of RF drain current that cannot respond to instantaneous gate modulations (a quantity that, when normalized to the steady-state drain current, has been called the gate-lag fraction<sup>[4]</sup>). In general, BV<sub>gd</sub> increases with gate-lag fraction. Our reported breakdown voltages correspond to a gate-lag fraction of less than 0.1. Chosen as such, these breakdown voltages correlate better with the PHEMT's power performance than BV<sub>gd</sub> alone.

The major tradeoff of this approach to power PHEMT was revealed by a delay time analysis. We employed the method of Moll et al<sup>[5,6]</sup> to decompose the components of the total delay time into the channel charging time and transit time, with the transit time obtained by measuring the total delay time as a function of the inverse drain current. The device's transit time was found to increase monotonically with the drain voltage, suggesting an increase in the effective gate length. At 7 volts of drain bias, this transit time accounts for more than 70% of the total delay time. This is clearly reflected in the drain bias dependence of Ft and Fmax as shown in Figure 3. Hence when biased for power operation, the highest possible operating frequency is limited by the electron transit time across the spread of the depletion layer at the drain end of the gate.

A PHEMT power transistor with simultaneous power output, gain and power-added efficiency has been demonstrated. The results of this work suggest that, in addition to superior low-noise performance, the PHEMT is also very promising for high-performance, power applications in the X- to Ku-band frequency range.

### Acknowledgement

The authors would like to thank T. Kazior, A. Palevsky, M. Cobb, L. Holway, R. Pucel and Prof. H. Hause of MIT for many useful discussions, R. Aucoin for E-beam lithography, J. Neyland for CAD support, A. Miquilarena and C. Bedard for processing, and R. Wohlert, B. McDonald, S. Nash, M. Niedzwiecki and G. Flynn for measurement assistance. We are grateful for the support and encouragement of P. Mumford and R. T. Kemerley. This work was in part sponsored by Wright Research and Development Center, US Air Force Wright-Patterson Air Force Base, Contract Number F33615-88-C-1743.

**Figure 1** A schematic of the gate-drain region of the high-breakdown pseudomorphic HEMT. The gate length is 0.33  $\mu$ m; the ungated recess area (covered by open circles depicting traps) is 0.3  $\mu$ m wide; and the gate-drain spacing is 1.1  $\mu$ m.

| 10 GHz   |           |           |             |                      |                                            |  |

|----------|-----------|-----------|-------------|----------------------|--------------------------------------------|--|

| Device   | PAE (%)   | Gain (dB) | Power (mW)  | P/gate width (mW/mm) | Comments (Reference)                       |  |

| HB-PHEMT | <u>65</u> | 11.8      | 312         | 780                  | 0.4-mm gate periphery                      |  |

| HB-PHEMT | 63        | 12.2      | <u>352</u>  | 880                  | 0.4-mm gate periphery                      |  |

| HB-PHEMT | <u>62</u> | 8.8       | 871         | 726                  | 1.2-mm gate periphery*                     |  |

| HB-PHEMT | 56        | 8.9       | <u>1120</u> | 935                  | 1.2-mm gate periphery*                     |  |

| MESFET   | 59        | 10.4      | 130         | 330                  | [7]                                        |  |

| HEMT     | 61        | 13.4      | 30          | 370                  | [8]                                        |  |

| HBT      | 68        | 11.6      | 223         | -                    | 80- $\mu\text{m}^2$ total junction area[9] |  |

| 18 GHz   |           |           |            |                      |                            |  |

|----------|-----------|-----------|------------|----------------------|----------------------------|--|

| Device   | PAE (%)   | Gain (dB) | Power (mW) | P/gate width (mW/mm) | Comments (Reference)       |  |

| HB-PHEMT | <u>51</u> | 7.6       | 300        | 750                  | 0.4-mm gate periphery      |  |

| HB-PHEMT | 47        | 7.4       | <u>348</u> | 870                  | 0.4-mm gate periphery      |  |

| PBT      | 40        | 6.6       | 72         | -                    | 20 GHz; [10]               |  |

| HEMT     | 42        | 6         | 36         | 480                  | 20 GHz; [8]                |  |

| PHEMT    | 55        | 9         | 72         | 480                  | 20 GHz; Doped Channel [11] |  |

| PHEMT    | 49        | 10.2      | 120        | 800                  | 20 GHz; Doped Channel [11] |  |

| HBT      | 48.5      | 6.2       | 170        | -                    | Common-Emitter; [12]       |  |

| HBT      | 47        | 11.3      | 218        | -                    | Common-Base; [12]          |  |

| HBT      | 43        | 11.4      | 358        | -                    | Common-Base; [12]          |  |

Note: 1)The underlined parameters were optimized during measurements. 2)The PHEMT presented in this work is auspiciously dubbed as the High-Breakdown PHEMT (HB-PHEMT).

\* The 1.2-mm device is slightly different from the device described in the text. The 1.2-mm device has a 0.4- $\mu\text{m}$  length, trapezoidal cross-section gate, and its epitaxial structure does not include an AlGaAs buffer.

**Table 1** A comparison of the state-of-the-art power transistors in published literature, with particular emphasis on the power-added-efficiency.

**Figure 2a, 2b** Pulsed I-Vs of a wide-recessed, pulse doped PHEMT with 0.33- $\mu\text{m}$  gate length and 400- $\mu\text{m}$  total gate periphery. These two figures show the bias dependent pulsed I-Vs of a device besieged by surface charge. This effect is the cause of poor power performance of pulse doped PHEMTs with wide gate recess. The quiescent bias voltages are indicated in the figure. The pulse duration is 220 ns for the gate and 170 ns for the drain; the pulse repetition rate is 90 Hz.

**Figure 2c, 2d** Pulsed I-Vs of the high-breakdown PHEMT with 0.33- $\mu$ m gate length and 400- $\mu$ m total gate periphery. The bias dependence is clearly removed. The pulsing condition is identical to that in a) and b).

**Figure 3** Current-gain cut-off frequency ( $F_t$ ) and maximum-available-gain cut-off frequency ( $F_{max}$ ) versus drain voltage behavior of a 100- $\mu$ m periphery high-breakdown PHEMT. The decrease in gain is correlated with an increase in the drain transit time.

## References

- [1] A. Platzker et al., "Characterization of GaAs Devices by a Versatile Pulsed I-V Measurement System," 1990 IEEE MTT-S International Microwave Symposium Digest.

- [2] J. C. Huang et al, "Parasitic Gating by Charged Surface States in Wide-Recessed AlGaAs/InGaAs Pseudomorphic High Electron Mobility Transistors," to be submitted for publication.

- [3] T. M. Barton and P. H. Ladbrooke, "The Role of the Device Surface in the High Voltage Behavior of the GaAs MESFET," Solid State Electronics Vol. 29, No. 8, pp. 807-813, 1986.

- [4] R. Yeats et al., "Gate Slow Transients in GaAs MESFETs--Causes, Cures and Impact on Circuits," IEEE IEDM 1988 Digest, pp. 842-845.

- [5] N. Moll et al, "Pulsed Doped AlGaAs/InGaAs Pseudomorphic MODFETs," IEEE Trans. Electron Devices, vol. 35, pp. 878-886, July 1988.

- [6] T. Enoki, K. Arai, and Y. Ishii, "Delay time analysis for 0.4- to 5- $\mu$ m-Gate InAlAs-InGaAs HEMT's," IEEE Elect. Dev. Lett., Vol. 11, No. 11, pp 502-504, 1990.

- [7] R. P. Smith et al, "Impulse-doped GaAs Power FETs for High Efficiency Operation," Electronic Letters, Vol. 24, No. 10, 1988.

- [8] P. Saunier and J. W. Lee, "High-Efficiency Millimeter-Wave GaAs/GaAlAs Power HEMT's," Elect. Dev. Lett., Vol. 7, No. 9, 1986.

- [9] N. L. Wang et al, "Ultrahigh Power Efficiency Operation of Common-Emitter and Common-Base HBT's at 10 GHz," IEEE Microwave Theory and Techniques, vol. 38, no. 10, 1990.

- [10] K. B. Nichols et al., "High Power-Added Efficiency Measured at 1.3 GHz and 20 GHz Using a GaAs Permeable Base Transistor," in Proc. 11th Biennial Conf. Adv. Concepts in High-Speed Semiconductor Devices and Circuits (Cornell Univ., Ithaca, NY), Aug. 1987.

- [11] P. M. Smith et al., "Microwave and mm-Wave Power Amplification Using Pseudomorphic HEMTs," Microwave Journal, May 1990.

- [12] N. L. Wang et al., "18 GHz High Gain, High Efficiency Power Operation of AlGaAs/GaAs HBT," 1990 IEEE MTT-S International Microwave Symposium Digest, pp 997.